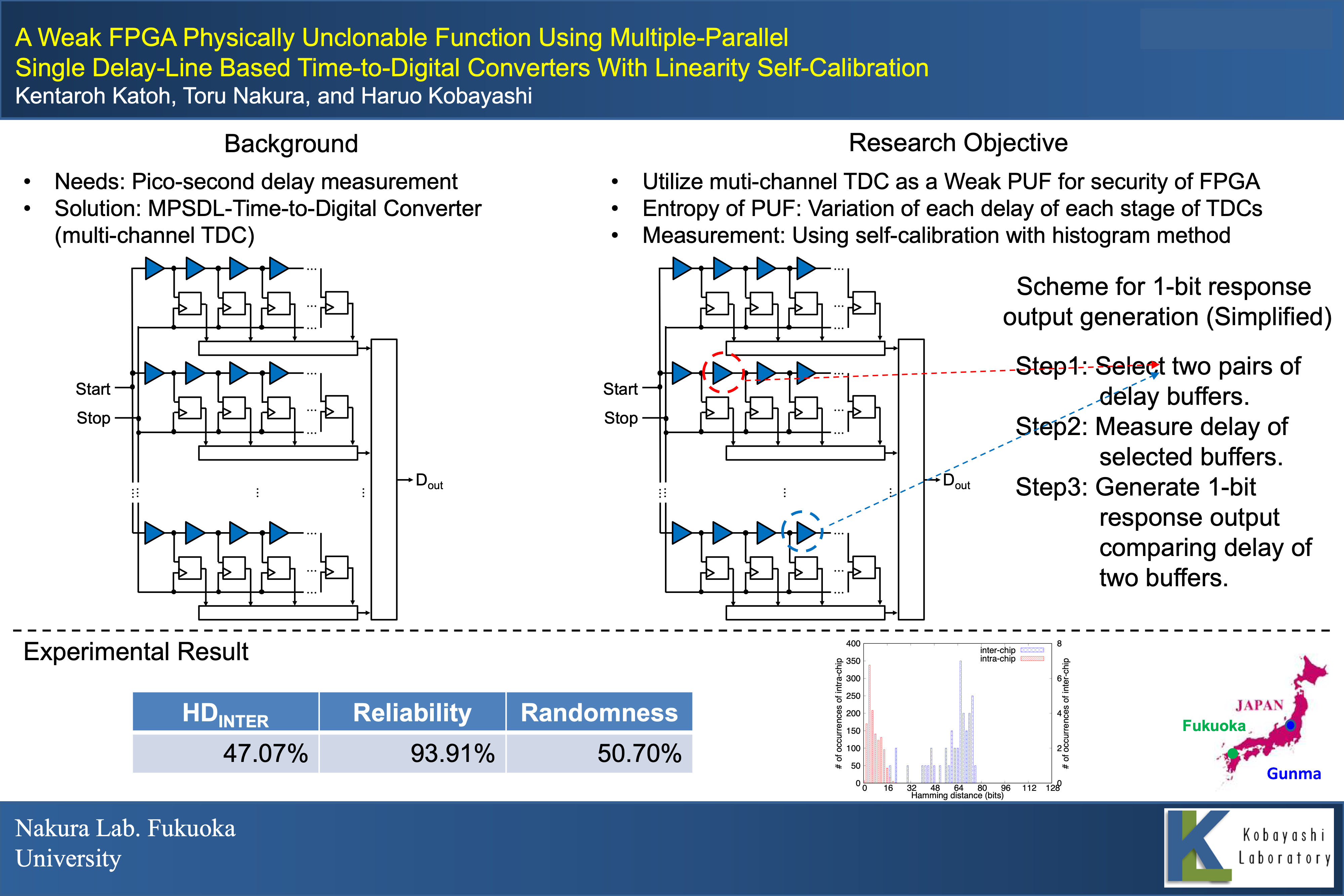

A weak FPGA physically unclonable function using multiple-parallel single delay-line based time-to-digital converters with linearity self-calibration

- Volume

- CitationKatoh K, Nakura T, Kobayashi H. A weak FPGA physically unclonable function using multiple-parallel single delay-line based time-to-digital converters with linearity self-calibration. Electron. Signal Process. 2026(1):0001, https://doi.org/10.55092/esp20260001.

- DOI10.55092/esp20260001

- CopyrightCopyright2026 by the authors. Published by ELSP.

- Special Issue

This paper presents a Weak Field-Programmable Gate Array Physically Unclonable Function (FPGA PUF) using Multiple Parallel Single Delay-Line based Time-to-Digital Converter (MPSDL-TDC) on FPGA. In the measurement mode, the proposed PUF works as a high-resolution FPGA TDC with the MPSDL-TDCs. In the PUF mode, the proposed PUF selects a stage of a TDC in the MPSDL-TDC and another stage of another TDC in it. Next, we calculate the buffer delays of the selected stages with the linearity self-calibration. Finally, we obtain a 1-bit response output by comparing the buffer delays. With a small amount of circuit, the proposed PUF can be applied to any type of MPSDL-TDCs, even it is the one with Look-Up Table (LUT) chain based TDCs or with the dedicated carry-chains based TDCs. Consequently, the number of the extra resources for the proposed PUF is small. Evaluation using 10 Artix-7 FPGAs resulted in an inter-chip Hamming distance of 47.07%, a reliability of 93.91%, and a uniformity of 50.70%. Minimum resource overhead for the proposed PUF over original MDSDL-TDCs is 4.99%.

PUF; weak PUF; hardware security; TDC; FPGA; MPSDL-TDC

X

X Facebook

Facebook LinkedIn

LinkedIn Reddit

Reddit Bluesky

Bluesky